随着SoC(System on Chip)架构的小型化面临困境,Chiplet技术备受关注。下面来说说chiplet技术三大重要标准。

SoC(System on Chip)架构的小型化面临着困境。这为通常称为“小芯片”的异构单封装系统中芯片间互连铺平了道路。尽管这种小芯片优化互连技术正在获得巨大的关注,但它仍处于起步阶段。

因此,小芯片之间的互连标准对于新的多芯片半导体时代变得至关重要。以下是在当前小芯片发展过程中被认为重要的三个标准的概述。这些标准预计将在构建开放的chiplet生态系统中发挥重要作用。

1、电线束(BoW)

线束 (BoW) 互连技术定义了单个封装内一对芯片到芯片 (D2D) 之间的开放、可互操作的物理接口。该技术定义了一个针对 SoC 分区进行优化的物理层 (PHY),并构成小芯片多芯片互连的基础。

美国初创公司 Eliyan Corporation 的创始首席执行官 Ramin Farjadrad 开发了专有的互连技术,该技术将构成 BoW 的基础,并于 2018 年成立了一家旨在提供高效硬件技术的合资企业。我们提出了该技术的标准化到社区“开放计算项目(OCP)”。该技术后来被 OCP 采用作为小芯片互连方案。

2、通用 Chiplet 互连 Express (UCIe)

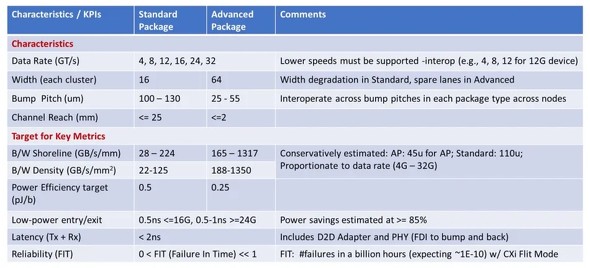

通用 Chiplet Interconnect Express (UCIe) 是芯片间连接的开放行业标准,由 80 多家公司组成的联盟开发,其中包括半导体和封装公司、代工厂、云服务和知识产权 (IP) 供应商。 2022 年。三月宣布。这是迈向多芯片系统异构集成的重要一步,该联盟旨在为半导体小芯片创建一个新的设计生态系统。

UCIe 在封装级别提供即插即用互连,简化了采用不同供应商的不同工艺技术的芯片之间的互操作性。它基于与 BoW 互连相同的信令和时钟方案以及架构基础,并且 UCIe 1.1 规范目前可用。

3、高带宽内存 (HBM)

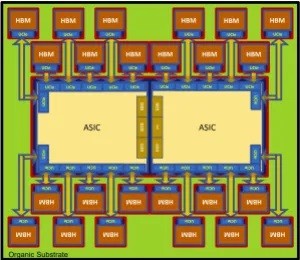

虽然严格来说它并不是一个小芯片标准,但它正在成为小芯片设计中的一个重要元素,因为它允许在更小的空间中封装更多的存储芯片。HBM 允许使用称为硅通孔 (TSV) 的垂直通道将不同层的存储芯片堆叠在彼此的顶部。它最初的设计目的是减少数据在内存和处理器之间传输的距离。

HBM 最初是为数据中心和云计算中的计算密集型应用而设计的,但其垂直堆叠 DRAM 芯片的能力现在使其成为与小芯片设计高度相关的技术。因此,一些新的chiplet解决方案不仅支持HBM协议,还支持UCIe。

-

2024-06-12

-

2024-06-03

-

2024-05-22

-

2024-05-22

-

2024-05-09