NMOS的驱动电路图及工作原理是怎么样的?

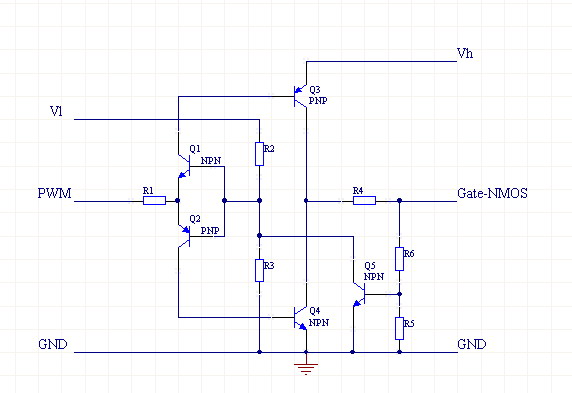

用于NMOS的驱动电路图及工作原理详解 这个电路提供了如下的特性: 1,用低端电压和PWM驱动高端MOS管。 2,用小幅度的PWM信号驱动高gate电压需求的MOS管。 3,gate电压的峰值限制 4,输入和输出的电流限制 5,通过使用合适的电阻,可以达到很低的功耗。 6,PWM信号反相。NMOS并不需要这个特性,可以通过前置一个反相器来解决。 电路图如下:  图1 用于NMOS的驱动电路 下面对NMOS驱动电路原理做一个简单分析: Vl和Vh分别是低端和高端的电源,两个电压可以是相同的,但是Vl不应该超过Vh。 Q1和Q2组成了一个反置的图腾柱,用来实现隔离,同时确保两只驱动管Q3和Q4不会同时导通。 R2和R3提供了PWM电压基准,通过改变这个基准,可以让电路工作在PWM信号波形比较陡直的位置。 Q3和Q4用来提供驱动电流,由于导通的时候,Q3和Q4相对Vh和GND最低都只有一个Vce的压降,这个压降通常只有0.3V左右,大大低于0.7V的Vce。 R5和R6是反馈电阻,用于对gate电压进行采样,采样后的电压通过Q5对Q1和Q2的基极产生一个强烈的负反馈,从而把gate电压限制在一个有限的数值。这个数值可以通过R5和R6来调节。 最后,R1提供了对Q3和Q4的基极电流限制,R4提供了对MOS管的gate电流限制,也就是Q3和Q4的Ice的限制。必要的时候可以在R4上面并联加速电容。

图1 用于NMOS的驱动电路 下面对NMOS驱动电路原理做一个简单分析: Vl和Vh分别是低端和高端的电源,两个电压可以是相同的,但是Vl不应该超过Vh。 Q1和Q2组成了一个反置的图腾柱,用来实现隔离,同时确保两只驱动管Q3和Q4不会同时导通。 R2和R3提供了PWM电压基准,通过改变这个基准,可以让电路工作在PWM信号波形比较陡直的位置。 Q3和Q4用来提供驱动电流,由于导通的时候,Q3和Q4相对Vh和GND最低都只有一个Vce的压降,这个压降通常只有0.3V左右,大大低于0.7V的Vce。 R5和R6是反馈电阻,用于对gate电压进行采样,采样后的电压通过Q5对Q1和Q2的基极产生一个强烈的负反馈,从而把gate电压限制在一个有限的数值。这个数值可以通过R5和R6来调节。 最后,R1提供了对Q3和Q4的基极电流限制,R4提供了对MOS管的gate电流限制,也就是Q3和Q4的Ice的限制。必要的时候可以在R4上面并联加速电容。

声明:本文来自【火眼甄芯】,未经允许,禁止转载,否则依法追究法律责任;文中图片部分来自于互联网,如有侵权,请联系删除,邮箱:2150693245@qq.com。

最新内容

-

2024-06-12

-

2024-06-03

-

2024-05-22

-

2024-05-22

-

2024-05-09